Cadence Virtuoso Liberate

Cadence Virtuoso Liberate用于设计全定制集成电路的工具;包括原理图输入、行为建模 (Verilog-AMS)、电路仿真、定制布局、物理验证、提取和反注释。 主要用于模拟、混合信号、RF 和标准单元设计,也用于存储器和 FPGA 设计。

用图形桌面模式如何提交任务

一、 提交流程

登录 Fastone 平台控制台;

数据管理上传计算文件;

在首页,点击【提交作业】-点击【ANSYS HFSS】应用-选择图形桌面模式-选择机器配置,进行启用机器;

上传计算文件,设置资源参数;

二、单机模式

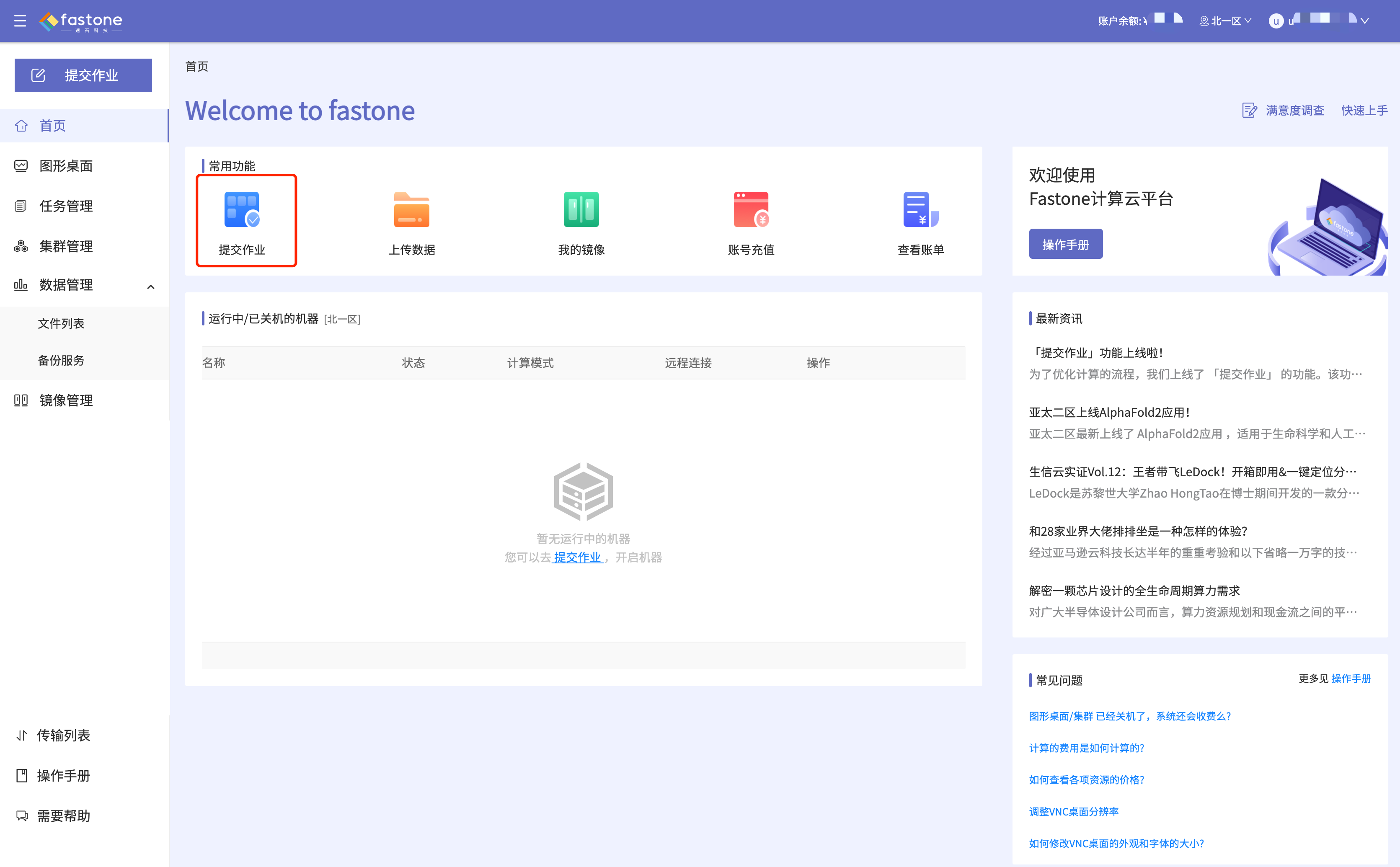

Step 1:首页选择【提交作业】,如图:

Step 2:选择【Cadence Virtuoso 】进行启用,如图:

可以选择社区应用,选择【Cadence Virtuoso】

社区应用为用户自发分享的应用,有可能会启用失败。

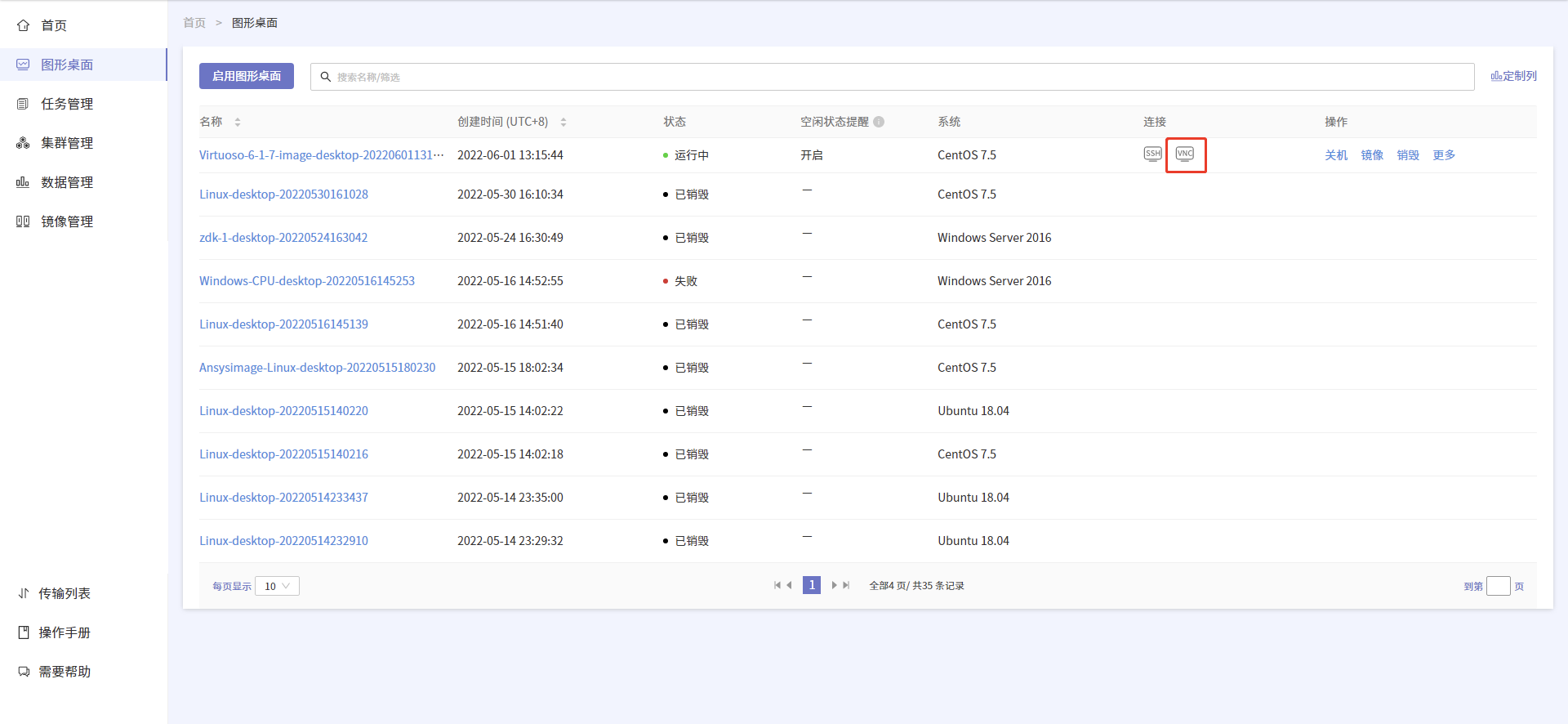

Step 3:在图形界面,选择创建的图形桌面,点击【VNC】

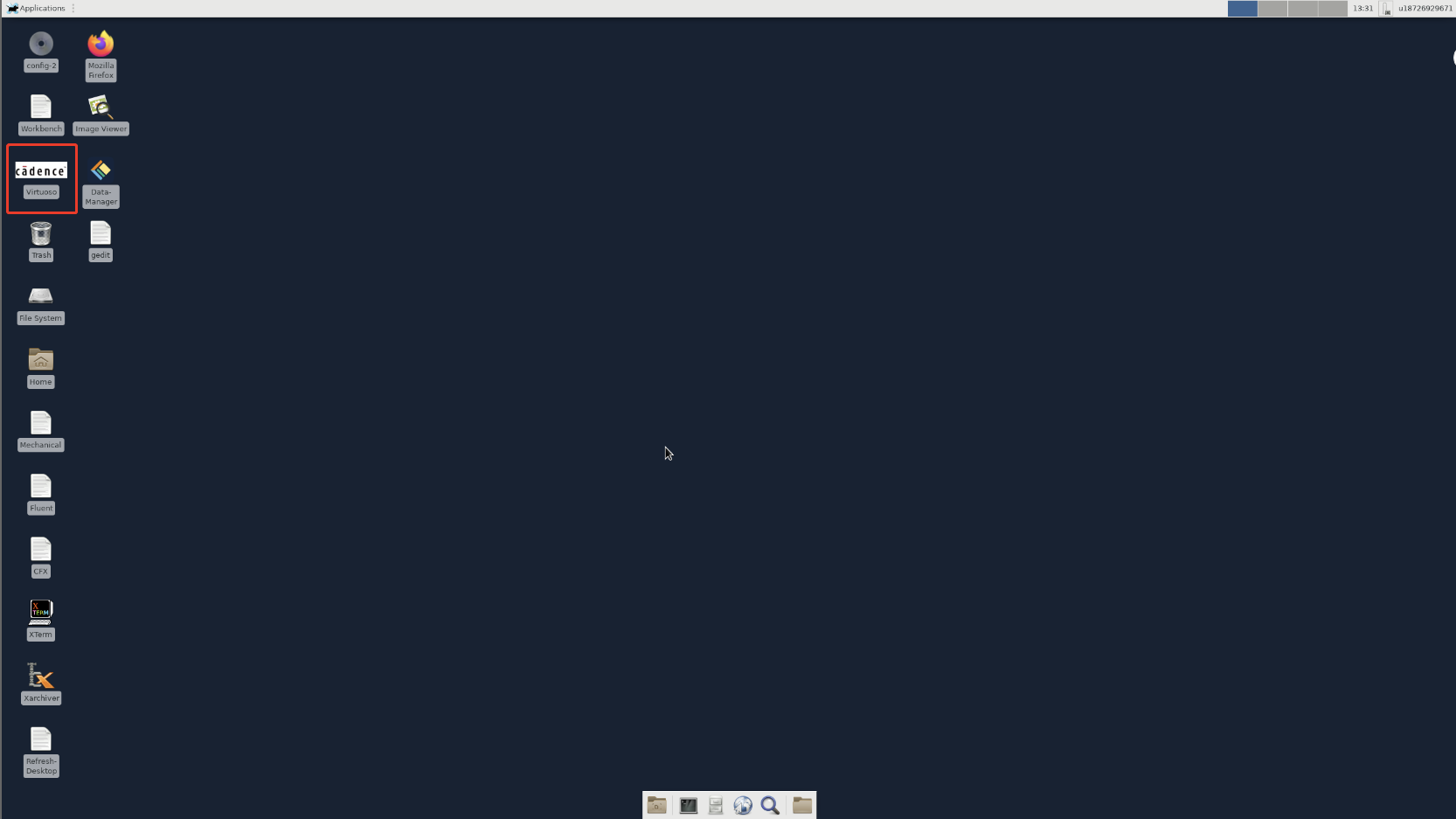

Step 4:进入【VNC】界面,在桌面打开virtuoso如图:

注意:第一次启动要等待两到三分钟。

- 等待几分钟后,会有提示环境配置完成,如图:

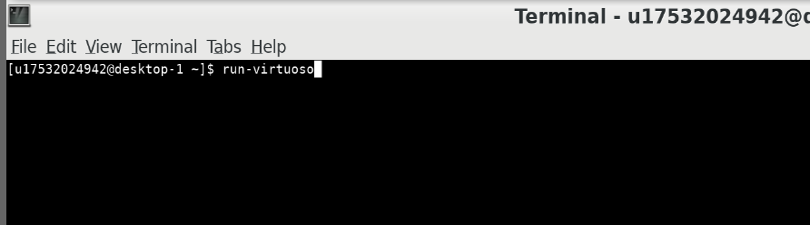

- 也可通过命令行方式唤起virtuoso,进入VNC远程连接后,打开terminal应用,然后执行执行run-virtuoso,会唤起virtuoso;

Step 5:提交后的监控

(1) 可通过图形桌面查看正在运行的计算节点资源使用率等信息。

(2) vnc连接到机器上,使用top,iostat,vmstat这些linux工具进行监控